### INTERNATIONAL CONFERENCE of SCIENTIFIC PAPER AFASES 2012 Brasov, 24-26 May 2012

### TIMING COMPUTING IN ASYNCHRONOUS DIGITAL AUTOMATA

#### Mihai TIMIS, Alexandru VALACHI

Technical University "Gh. Asachi" Iasi, Automatic Control and Computer Science Faculty, Computer Science departament mtims@cs.tuiasi.ro, avalachi@cs.tuiasi.ro

**Abstract:** In present paper, the authors has proposed a new idea for synthesis of an asynchronous digital system, using locally clock method. Driving an asynchronous digital system is much complex than a synchronous one. The authors has proposed a new method for synthesis of an asynchronous digital system using Verilog HDL Hardware Description Language, and also, the implementation into FPGA (Field Programable Gate Arrays) devices, [1-4]. The proposed method presented in this paper has many execution speed much better, maximize the combinational/sequential digital logic, maximize the design performances (speed, low power, size). The CK and the output signals must be free of logic hazard; The minimum propagation delay of CK signal through the digital combinational system must be greater than the maximum propagation delay for every logic circuit which implements the input/output signals. Once the CK signal is triggered it can be reseted without digital hazard. Using the improved design described above, the entire asynchronous digital system will work with work correctly.

Keywords: Digital logic, FSM, Verilog HDL, Transition Table, ModelSim, Timing computations.

### 1. INTRODUCTION

Driving an asynchronous digital system is a such complex task instead synchronous systems. The authors propose a method for synthesis of the asynchronous digital systems using Verilog HDL, and implement them into a FPGA devices, [1,2,3]. The proposed method presented in this paper has many features like:

- execution speed much better;

- maximize the combinational/sequential digital logic

- maximize the design performances (speed, low power, size)

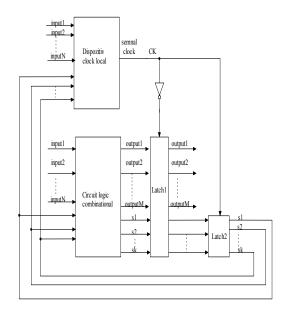

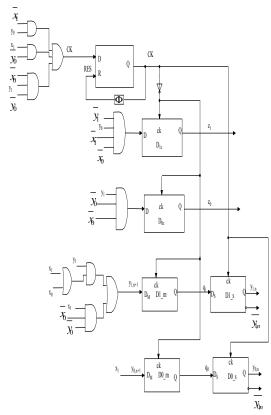

A such of system is presented in figure 1. It contains the combinational logic modules, D latches, input signals input1,input2...inputN, output signals named output1,output2....outputM, state variables named s1,s2...sk. The combinational system which implements an internal drive in signal. it is used for control the states of the digital system, disposal the hazard phenomenon from the digital systems. The entire system transit into a new state driving by the input signals which need to be stabile a period of time before changed and by the present states of the system.

Fig.1. Digital Asynchronous System

In figure 1 it's shown the consist modules of the digital system:

- drive in signal device;

- combinational system who implements the system states equation;

- D type latch1, latch2 are used to memorise the state of the system and also the outputs of the system;

The drive in signal (1) depends by the system's states notated with  $Q_i$ , input signals notated with  $X_j$ , where i=1,2,...n-1, j=1,2,...m-1; (n- states number variables, minput number variables).

$$CK = F(Q_i, X_i) \tag{1}$$

If signal CK=1 the system will go onto a new state, if CK=0 the system will stay in present state, it will can read the output values signals. While the states and outpus signals are computed, the input signals will not be changed, the system will work in fundamental mode.

### 2. DESIGN OF ASYNCHRONOUS DIGITAL SYSTEM WITH LOCALLY CLOCK METHOD

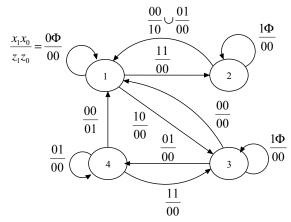

Let's consider an asynchronous digital system with functionality described by the fluence graph, figure 2:

Figure 2. Graph table

The fluence table is described in figure 3.

| $Q_{n+1}/z_1z_0$   |      |      |      |      |  |  |

|--------------------|------|------|------|------|--|--|

| $(x_1x_0)_n$ $Q_n$ | 00   | 01   | 11   | 10   |  |  |

| 1                  | 1/00 | 1/00 | 2/00 | 3/00 |  |  |

| 2                  | 1/10 | 1/00 | 2/00 | 2/00 |  |  |

| 3                  | 1/00 | 4/00 | 3/00 | 3/00 |  |  |

| 4                  | 1/01 | 4/00 | 3/00 | -/   |  |  |

Fig.3. Fluence graph table

The equations are like, (2):

$$D_{1} = y_{1,n+1} = [y_{1}(x_{0} + x_{1}) + \overline{y_{0}}x_{1}\overline{x_{0}}]_{n}$$

$$D_{0} = y_{0,n+1} = x_{1,n}$$

$$z_{1,n} = (\overline{y_{1}}y_{0}\overline{x_{1}}\overline{x_{0}})_{n}$$

$$z_{0,n} = (y_{1}\overline{y_{0}}\overline{x_{0}})_{n}$$

(2)

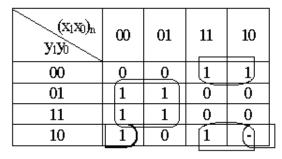

The CK truth table is deducted from fig.3, like in fig.4:

Fig. 4. CK truth table

Using the Veitch-Karnaugh, method it will compute the CK's equation (3):

$$CK = \overline{x_1} y_0 + x_1 \overline{y_0} + \overline{x_0} y_1 \overline{y_0}$$

(3)

## INTERNATIONAL CONFERENCE of SCIENTIFIC PAPER AFASES 2012

Brasov, 24-26 May 2012

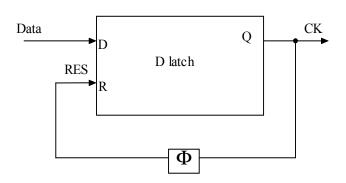

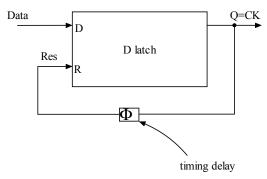

## The D flip-flop circuits are described in fig.5:

Fig.5. D flip-flop

$z_1$ ,  $z_0$  - represents the outputs of the system  $y_1$ ,  $y_0$  - represents the state of the system

The output signals  $z_1$ ,  $z_0$  and state signals  $y_1$ ,  $y_0$ , has attached a D flil-flop latch. The D flip-flop latch1 stores the output signals while the latch2 stores the states signals. They are triggered on the positive clock signal – CK. After a delay time, the CK signal is reseted who let the latch1 to be triggered.

The design of the proposed system is like in fig. 6.

Fig 6. Design with D flip-flop

The entire digital system must meet the following restrictions:

- The minimum propagation delay of CK signal through the combinational system must be greater than the maximum propagation delay for every logic circuit which implements the input/output signals.

- Once the CK signal is triggered it can be reseted without digital hazard.

- Using the improved design described above, the entire asynchronous digital system will work concordant with the specifications.

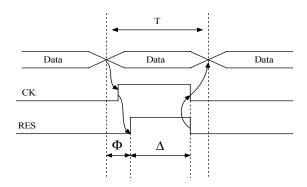

- For a corect functionality, the following conditions must meet, fig.7.

$$\begin{aligned} \Phi &<< T \\ \Phi + \Delta &= T \\ \Delta &\leq T \\ \Delta &> \Phi \end{aligned}$$

Fig 7. Functionality diagram

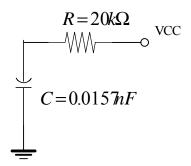

- If we set the value of delay time for the Q to Res signal  $\Phi = 314ns$ , we can use a RC circuit like:

Fig. 8. RC circuit

Using the Fairchild Semiconductor Data Book, for the logic gates AND, OR, INV, D latch, can be deducted the following time requirements, fig.6:

| Gate type    | $\mathrm{TP}_{\mathrm{LH}}$ | $\mathrm{TP}_{\mathrm{HL}}$ |

|--------------|-----------------------------|-----------------------------|

| AND 2 inputs | 7.6ns                       | 8.8ns                       |

| AND 3 inputs | 18ns                        | 14ns                        |

| AND 4 inputs | 7.6                         | 8.8ns                       |

| OR 3 inputs  | 11.4ns                      | 7.4ns                       |

| OR 2 inputs  | 10ns                        | 14ns                        |

| D latch  | 8.5ns | 13ns |

|----------|-------|------|

| Inverter | 9.0ns | 13ns |

Figura 9. D latch logic cell

When TP<sub>LH</sub> propagation time is taken into consideration, we have:

D\_CK - the combinational digital logic implementation:

$$2 \cdot AND(2in) + 1 \cdot AND(3in) + 1 \cdot OR(3in) + 2 \cdot INV =$$

$$= 2 \cdot 7.6 + 1 \cdot 1.8 + 1 \cdot 11 + 2 \cdot 9 = 44.2 + 18 = 62.2ns$$

(4)

$D_1$  - the combinational digital logic implementation:

$$1 \cdot AND(4in) + 2 \cdot INV = 7.6 + 18 = 25.6ns$$

(5)

$D_0$  - the combinational digital logic implementation:

$$1 \cdot AND(3in) + 2 \cdot INV = 18 + 18 = 36ns$$

(6)

$y_{1,n+1}$ - the combinational digital logic implementation:

$$1 \cdot AND(2in) + 2 \cdot OR(2in) + 3 \cdot AND(3in) + 1 \cdot INV =$$

$$= 1 \cdot 7.6 + 2 \cdot 10 + 3 \cdot 18 + 9 = 81.6 + 9 = 90.6ns$$

(7)

The  $\Phi$  delay is compted with the next propagation delays,

# INTERNATIONAL CONFERENCE of SCIENTIFIC PAPER AFASES 2012

Brasov, 24-26 May 2012

$\Phi = T_{\rho(D_{-}CR)} + T_{\rho(D)} + T_{\rho(D)} + T_{\rho(D), t+1} + T_{\rho(D_{c})} =$  = 622 + 256 + 36 + 906 + 85 + 85 + 85 + 85 + 85 + 85 + 85 = 2654 ns

(8)

### 3. CONCLUSIONS

- The CK signal and the output signals must be free of logic hazard inorder to met the system run like within the specifications;

- The minimum propagation delay of CK signal through the combinational system must be greater than the maximum propagation delay for every logic circuit which implements the input/output signals.

- Once the CK signal is triggered it can be reseted without digital hazard.

- Using the improved design described above, the entire asynchronous digital system will work like in the specifications.

### 4. REFERENCES

- [1] Steven Mark Nowick . Automatic Synthesis of Burst-Mode Asynchronous Controllers. Technical Report, December 1995.

- [2] C. Roth. Principles of Fundamental Logic Design. New York, 1995.

- [3] Chris J. Myers. Asynchronous Circuit Design. John and Soons, Inc. 1995.

- [4] Alexandru Valachi, Radu Silion, <u>Mihai Timiş</u>. Improvement of FSM Synthesis using MSI and LSI circuits. 8<sup>th</sup> International Symposium on Automatic Control and Computer Science, Iasi, 2004.

- [5] Douglas J. Smith. HDL Chip Design. The Doone Publications 2001.

- [6] Verilog HDL Synthesis. A practical Primer. J.Basker, Doone Public.2000.